碳化硅衬底的生长与加工流程详解

作为第三代半导体材料的典型代表,碳化硅(SiC) 兼具宽禁带、高热导率、高击穿电场和高电子迁移率等优势, 是高压、高频、高功率器件的核心材料,被视为新能源电驱、 充电基础设施等领域的关键基础之一。 在功率器件的生产制造链条中,SiC 单晶衬底的生长和后续加工 是决定器件性能和良率的核心环节。

本文从工艺视角出发,对碳化硅衬底从单晶生长到终检放行的整体流程 进行系统梳理,帮助读者从“材料工程”的角度理解 SiC 衬底质量形成的全过程。

- 单晶生长:基于 PVT(改良 Lely)法的 SiC 晶体生长与籽晶管控;

- 晶锭加工:定向、外圆加工与多种切割技术对表面损伤的影响;

- 晶片加工:倒角、减薄 / 研磨与 CMP 化学机械抛光协同;

- 终检放行:清洗与颗粒 / 缺陷检测,衔接外延与器件制造。

一、SiC 单晶衬底的生长:PVT 改良 Lely 法

碳化硅晶体的制备最早可追溯到 1955 年的 Lely 升华技术, 当时获得的晶体尺寸有限、形状不规则且多晶型混杂,难以满足器件制造需求。 1978 年,Tairov 等在石墨坩埚上部低温区引入 SiC 籽晶, 成功解决了多晶成核问题,由此发展出今天广泛应用的 改良 Lely 法 / 物理气相传输法(PVT), 成为当前工业量产 SiC 单晶的主流路线。

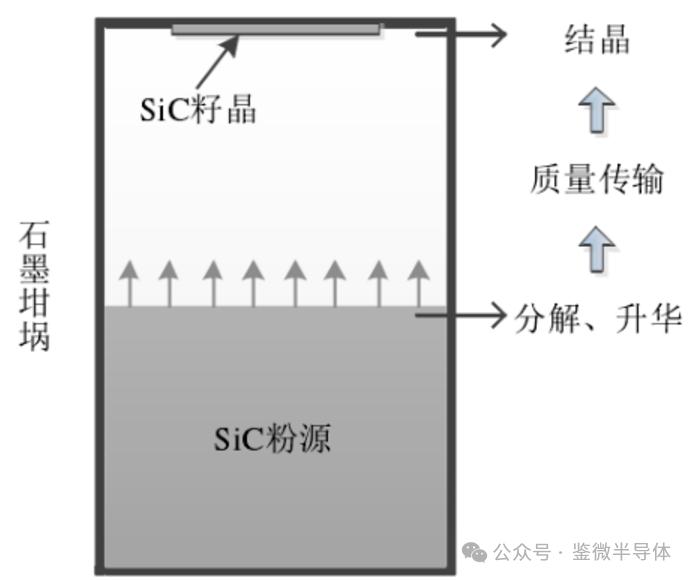

在典型的 PVT 生长炉中,SiC 粉源置于石墨坩埚底部,高温下分解并升华, 蒸气通过温度梯度传输到顶部籽晶区域,在籽晶生长面发生沉积结晶, 逐层长成大尺寸碳化硅单晶晶锭。 其中籽晶质量尤为关键:不仅需具备特定偏轴角(如 4°), 还需对面型、电阻率及多类生长 / 加工缺陷 (微管、多型、包裹、六方空洞、划痕、崩边等)进行严格筛选, 以保证晶体后续扩径与外延应用的稳定性。

在实际生长过程中,温度场分布、坩埚结构设计、原料纯度与籽晶摆放方式等因素相互耦合, 共同决定了单晶内部的缺陷分布与多型稳定性。 一旦在生长阶段出现大范围微管、层错或多型混杂,后续加工环节难以彻底消除, 极易在器件端演变为漏电、击穿电压不足等失效问题。

二、SiC 晶锭加工:从“黑饼”到标准圆柱

出炉后的 SiC 晶锭外形不规则,首先要经过 X 射线定向、滚外圆和磨平端面, 将晶锭加工成标准尺寸的光滑圆柱体,为后续晶片切割做准备。

在切割环节,目前行业主流包括:

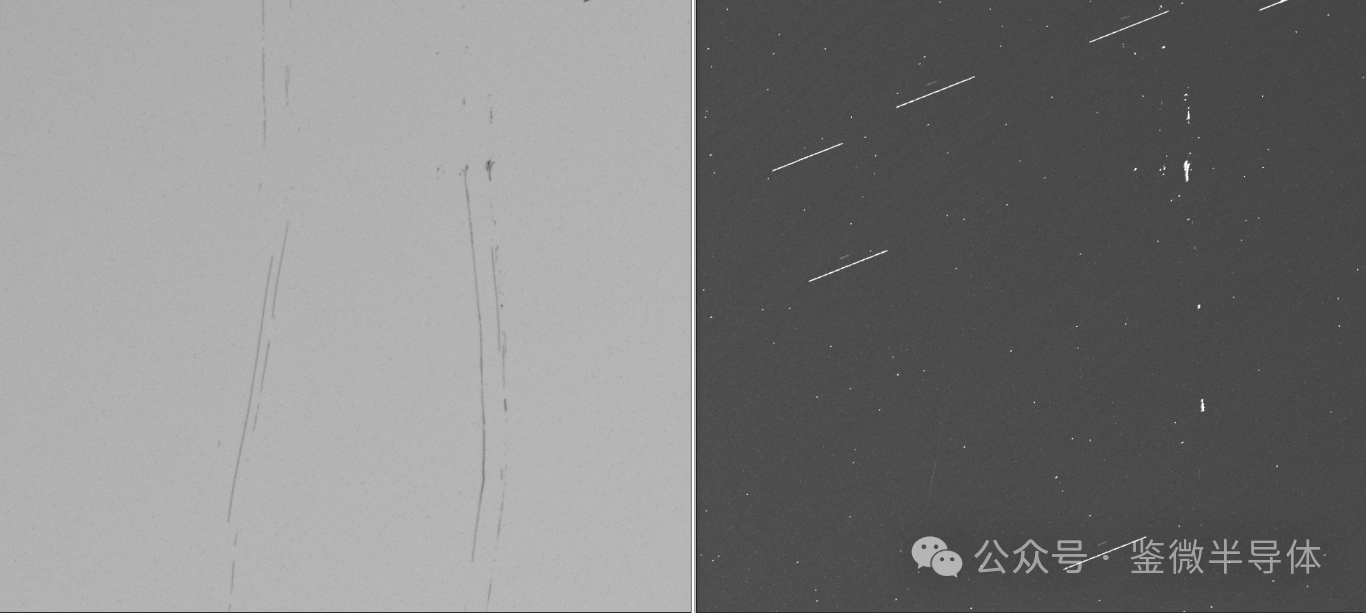

· 砂浆线切割: 利用含磨料的线与砂浆切割,工艺成熟、设备成本较低, 但切割速度慢,且易在衬底表面形成较深损伤层, 即便后续研磨 / CMP 也难以完全去除, 可能在外延工艺中“继承”为划痕、台阶线等缺陷。

· 金刚线切割: 以金刚石颗粒为磨料,通过高速运动的线实现切割, 具有速度快、损伤层较浅等优点,有利于提升衬底质量和成品率, 但材料损耗仍然较大,对线材工艺也提出更高要求。

· 激光剥离: 借助激光热效应实现精确分离,可显著降低机械损伤和材料浪费, 但目前设备成本及工艺成熟度仍在爬坡阶段, 尚处于向规模化应用过渡的过程之中。

不同切割工艺在成本、效率和损伤层深度之间存在权衡。 对于 6 英寸及以上大尺寸衬底,如何在保证良率的前提下降低总加工成本, 仍是业内持续优化的方向之一。

三、SiC 晶片加工:倒角、减薄 / 研磨与 CMP

切割后得到的 SiC 晶片在边缘存在较大应力, 若直接流入后续工序,极易在搬运和加工过程中产生崩边、裂纹等失效风险。 因此,首先需要对晶片边缘进行倒角, 将锋利边缘修整为指定圆弧形状,以降低局部应力集中。

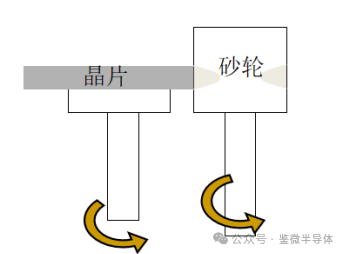

随后进入减薄 / 研磨阶段,通过粗磨与精磨逐步降低厚度、改善平坦度, 并去除早期工序遗留的部分损伤层。 传统研磨依赖研磨液,流程相对繁琐、自动化程度有限, 对大尺寸晶圆存在一定破片风险; 新一代减薄工艺则采用磨轮加工, 具备更高的材料去除效率与面型控制能力,更适配 6 英寸、8 英寸等大尺寸 SiC 晶圆, 但磨轮耗材成本仍然偏高。

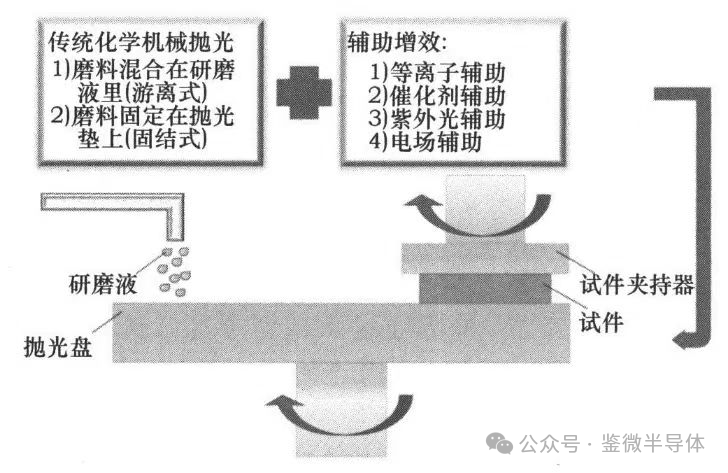

即便经过减薄 / 研磨,晶片表面仍存在浅表损伤, 需要依靠化学机械抛光(CMP)获得粗糙度小于 0.1 nm 的超光滑表面。 典型流程是先用高锰酸钾或双氧水等对表面损伤层进行氧化, 再借助氧化铝 / 氧化硅磨粒与抛光垫的机械摩擦, 逐层去除软化后的氧化层,最终获得接近“镜面”的衬底表面, 是 4H-SiC 衬底实现低缺陷外延的关键步骤。

为提升 CMP 的生产效率,行业也在探索多种增效技术, 如等离子体辅助、催化剂辅助、紫外光辅助、电场辅助等, 为未来高产能生产线预留了工艺升级空间。

四、终检放行:清洗与缺陷检测

CMP 结束后,SiC 晶圆表面的“断裂键”活性很强, 极易吸附颗粒、金属、有机物和湿气分子等污染物, 因此必须经过预清洗 + 终端清洗。 典型湿法清洗组合包括硫酸清洗液(SPM)、碱性清洗液(APM)、DHF 等, 常见终端清洗方案为 RCA 工艺, 目的是在保证金属离子和微颗粒受控的前提下, 为外延与器件工艺提供高洁净度衬底。

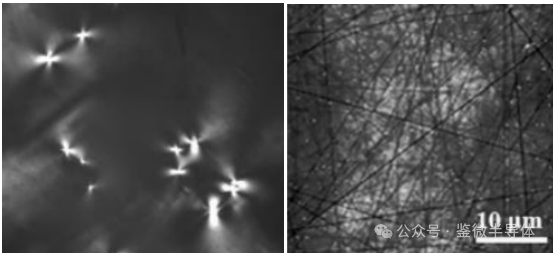

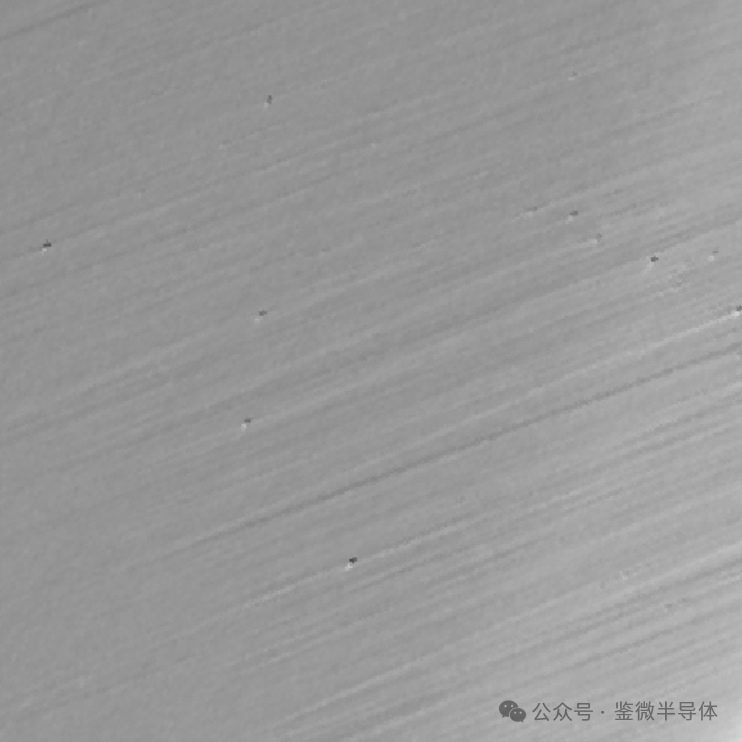

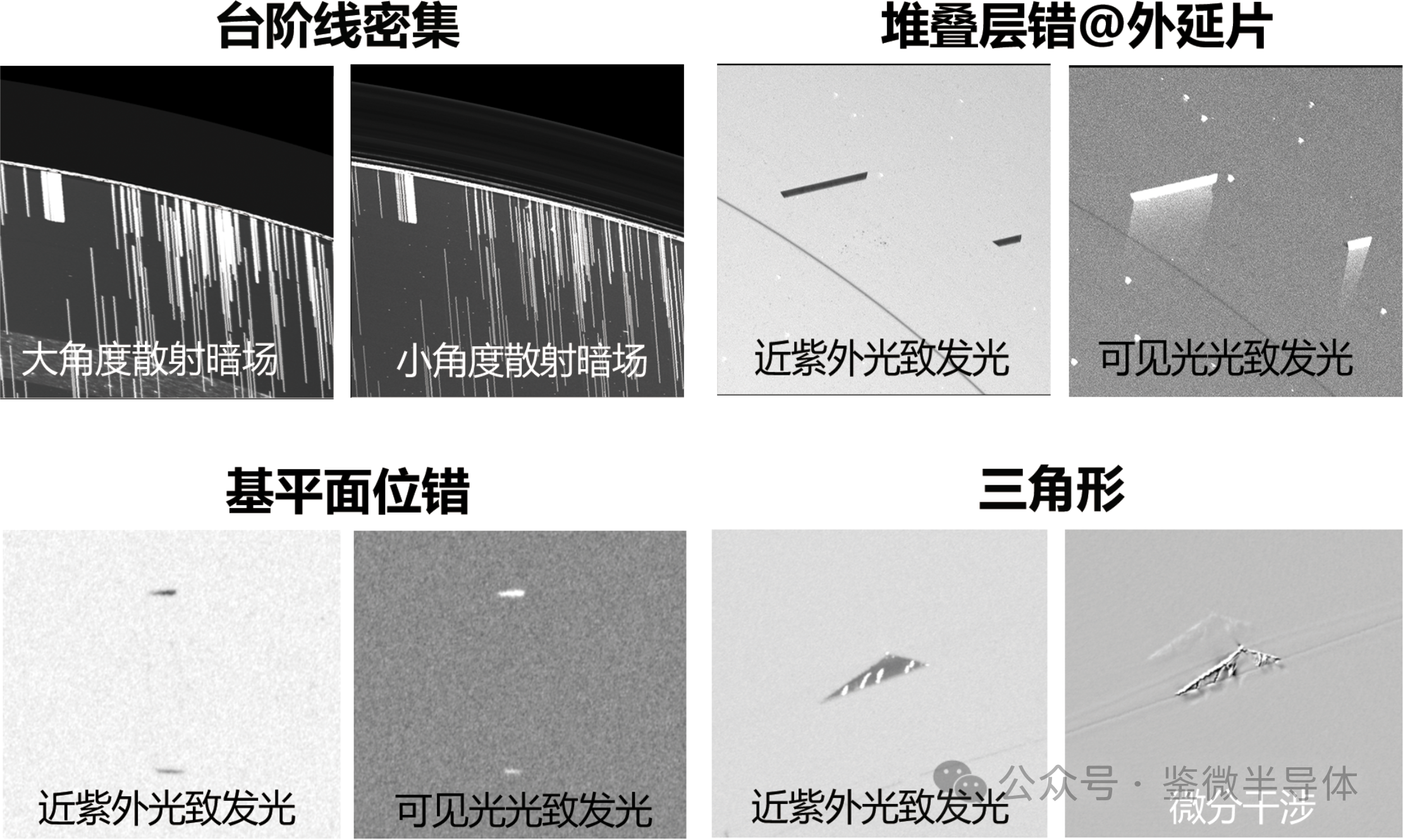

在检测环节,目前主流的衬底终检手段包括激光散射法与 共聚焦显微法, 不仅用于检测颗粒,还可识别 CMP 后的精细划痕、小微管、凹坑、 堆垛层错等各类缺陷,实现从衬底到外延缺陷之间的关联分析。

终检合格的碳化硅衬底晶片随后打包出货,进入外延生长与器件加工环节。 从生长炉中的 SiC 粉源,到外延线上的高压模块, 中间每一道检测关口,都在为第三代半导体器件的性能和可靠性“把最后一关”。

结语:从“材料工程”到“质量工程”

对于碳化硅衬底来说,生长工艺、机械加工、表面工程和检测技术 并非孤立存在,而是一个紧密耦合的系统工程: 任一环节的波动,都可能在外延乃至器件端被放大为良率与可靠性的“痛点”。

鉴微半导体将持续围绕 SiC 衬底的全流程检测需求, 在激光散射、光学显微、智能算法及系统集成等方向不断迭代产品与方案, 为第三代半导体产业提供更完整的检测与质量控制能力支撑。

关注公众号

Email:business@microinspect.tech

Add: 北京市海淀区中关村东路8号东升大厦C座223室

Copyright © 2025 uInspect 鉴微半导体 | All Rights Reserved 隐私政策